The difference between CPLD and FPGA are discussed in the article. But before that, some basic information about CPLD and FPGA is discussed below.

Table of Contents

Complex Programmable Logic Device (CPLD)

- Complex Programmable Logic Device (CPLD) is an erasable programmable logic device that can be programmed with a schematic or behavioral design.

- CPLD is nothing but a type of complex PLD based on EPROM or EEPROM technology.

- A basic CPLD cell is called a macrocell, which is the CPLD implementation of a CLB. It is composed of AND gate arrays and is surrounded by interconnect area.

- They are characterized by an architecture offering high speed, predictable timing, and simple software.

- Also referred to as multilevel arrays, devices that combine a number of PAL type circuits on the same chip.

- Logic blocks are programmable AND and fixed OR structure with fewer product terms than most PAL devices.

- PALs and GALs are available in small sizes, equivalent to a few hundred logic gates. For bigger circuits (logic), complex PLDs or CPLDs can be used.

- CPLDs can replace thousands or even hundreds of thousands of logic gates.

- Some CPLDs are programmed using a PAL programmer but this method results inconvenient for devices with hundreds of pins.

- The second method of programming is to solder the device to its printed circuit board, then feed it with a serial data stream from a personal computer.

- CPLD contains a circuit which decodes the data stream and configures the CPLD to perform its specified logic function.

Field Programmable Gate Arrays (FPGAs)

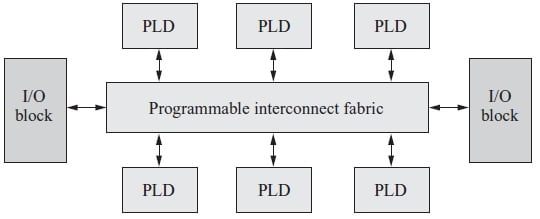

- FPGAs offer a number of configurable logic blocks (CLBs) which contains programmable combinational logic and registers for sequential circuits.

- There is also a set of input/output blocks that can be configured as fixed input, fixed output, or bidirectional.

- Outputs have tristate nature and registers can be used for latching incoming or outgoing data.

- FPGAs use a grid of logic gates, similar to that of an ordinary gate array, but programming is done by the customer, not by the manufacturer.

- In FPGA, all the configurable logic blocks and input/output blocks can be programmable interconnected to implement virtually any logic circuit.

- FPGAs are generally programmed after being soldered down to the circuit board, in the same way as larger CPLDs.

- In larger FPGAs, the configuration is volatile and must be re-loaded into the device whenever power is applied or different functionality is required.

Difference between CPLD and FPGA

| S.No. | CPLD | FPGA |

| 1 | CPLD stands for Complex Programmable Logic Device. | FPGA stands for Field Programmable Gate Array. |

| 2 | CPLD provide highest performance, but they also contain fewer registers than FPGAs. | FPGAs are offered in a wide density range, from few thousand gates to several million gates. |

| 3 | CPLDs are ideal for complex blocks with a large number of inputs. | FPGA architecture is more granular compared to CPLD, making it suitable for designs with large number of simple blocks with few numbers of inputs. |

| 4 | CPLDs can implement large functions in one pass through logic array. | FPGAs can’t implement large functions in one pass through the logic array. |

| 5 | CPLD’s resources are partitioned into logic blocks, imposing restrictions on how they may be used. | FPGAs contain arrays of logic cells and are less partitioned than CPLDs. |

| 6 | The number of input-output pins offered by CPLD is significantly higher. | A number of input-output pins offered on the FPGA are less than CPLD. |

| 7 | Any design can fit into a 100 K gate CPLD, i.e. space required on silicon is less. | The same design requires 150 K gate FPGA i.e. space required on silicon is more. |

| 8 | CPLD based design needs less board space, board layout complexity, cost and Bill Of Material (BOM) than FPGA. | FPGA based design needs increased board space, board layout complexity, cost and Bill Of Material (BOM). |

| 9 | CPLD doesn’t require any memory store configuration program. | FPGA invariably require one or more configuration PROM, depending on the size of FPGA used. |

| 10 | CPLDs with their course-grain architecture and dedicated routing offer the advantage of predictable timing and end-of-use. | Due to granular architecture and segmented routing of FPGAs, it is difficult to predict the speed performance of a design until it is targeted in the software. |

| 11 | CPLD consume more power than FPGA devices. | FPGA consumes less power than CPLD. |

| 12 | Process technologies are EPROM, EEPROM and FLASH. | Process technologies are SRAM, anti-fuse and EEPROM. |

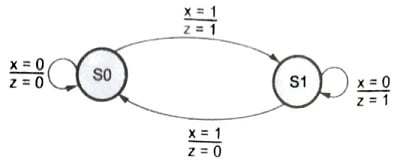

| 13 | Applications of CPLD bus interfaces, complex state machines, fast memory interfaces, wide detectors, PAL device integration. | FPGA applications Logic consolidation, board integration, replaces absolute devices, simple state machines, complex controllers/interfaces. |